## LAN91C100 ADVANCE INFORMATION

# FEAST™ Fast Ethernet Controller

#### **FEATURES**

- Dual Speed CSMA/CD Engine (10 Mbps and 100 Mbps)

- Compliant with IEEE 802.3 100BASE-T Specification

- Supports 100BASE-TX, 100BASE-T4, and 10BASE-T Physical Interfaces

- 32 Bit Wide Data Path (Into Packet Buffer Memory)

- Support for 32 and 16 Bit Buses

- · Support for 32, 16 and 8 Bit CPU Accesses

- Synchronous, Asynchronous and Burst DMA Interface Mode Options

- 128 Kbyte External Memory

- Built-in Transparent Arbitration for Slave Sequential Access Architecture

- Flat MMU Architecture with Symmetric Transmit and Receive Structures and Queues

- MII (Media Independent Interface)

Compliant MAC-PHY Interface (Compliant with Emerging MII Standard Interface)

- MII Management Serial Interface

- Seven Wire Interface to 10 Mbps ENDEC (LAN83C694)

- EEPROM-Based Setup

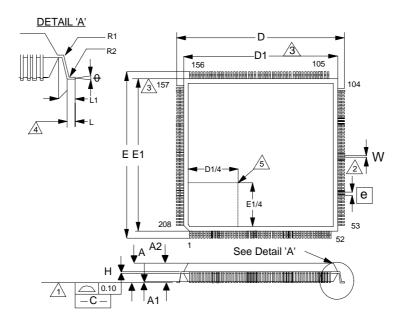

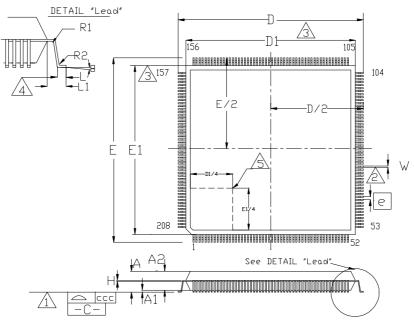

- 208 Pin PQFP and TQFP Package

#### **GENERAL DESCRIPTION**

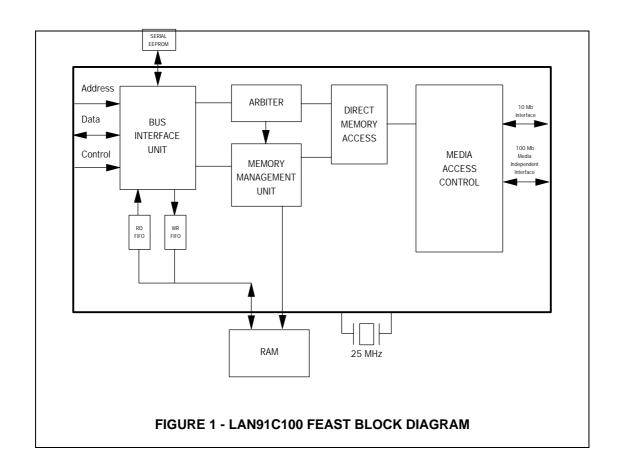

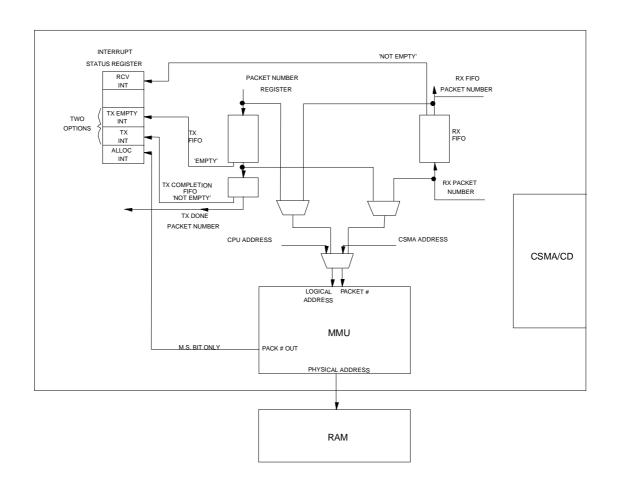

The LAN91C100 FEAST is a high-speed network controller designed to facilitate the implementation of Fast Ethernet adapters and connectivity products. It contains a dual speed CSMA/CD engine that implements the MAC portion of the CSMA/CD protocol at 10 and 100 Mbps and couples it with a lean and fast data and control path system architecture to ensure data movement with no bottlenecks at 100 Mbps.

Memory management is handled using a unique MMU (Memory Management Unit) architecture and a 32-bit wide data path. This I/O mapped architecture can sustain back-to-back frame transmission and reception for superior data throughput and optimal performance. It also

dynamically allocates buffer memory in an efficient buffer utilization scheme, reducing software tasks and relieving the host CPU from performing these housekeeping functions. The total memory size is 128 Kbytes (external), equivalent to a total chip storage (transmit and receive) of 64 outstanding packets.

FEAST provides a flexible slave interface for easy connectivity with industry-standard buses. The Bus Interface Unit (BIU) can handle synchronous as well as asynchronous buses, with different signals being used for each one. FEAST's bus interface supports synchronous buses like the VESA local bus, as well as burst mode DMA for EISA environments. Asynchronous bus support for ISA is supported

## **TABLE OF CONTENTS**

| FEATURES                      | 1  |

|-------------------------------|----|

| GENERAL DESCRIPTION           | 1  |

| PIN CONFIGURATION             | 3  |

| DESCRIPTION OF PIN FUNCTIONS  | 4  |

| FUNCTIONAL DESCRIPTION        | 14 |

| DATA STRUCTURES AND REGISTERS | 17 |

| BOARD SETUP INFORMATION       | 59 |

| APPLICATION CONSIDERATIONS    | 62 |

| OPERATIONAL DESCRIPTION       | 69 |

| MAXIMUM GUARANTEED RATINGS    | 69 |

| DC ELECTRICAL CHARACTERISTICS | 69 |

| TIMING DIAGRAMS               | 72 |

80 Arkay Drive Hauppauge, NY 11788 (516) 435-6000 FAX (516) 273-3123 even though ISA cannot sustain 100 Mbps traffic. Fast Ethernet could be adopted for ISA-based nodes on the basis of the aggregate traffic benefits.

FEAST is software-compatible with the existing LAN9000 family of products and can use current LAN9000 drivers in 16- and 32-bit Intel X86-based environments.

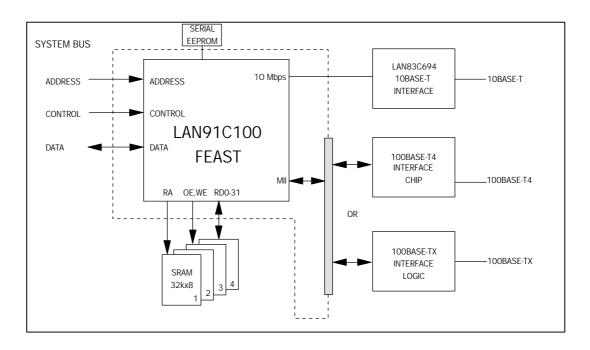

Two different interfaces are supported on the network side. The first is a conventional seven

wire ENDEC interface that connects to the LAN83C694 for 10BASE-T and coax 10 Mbps Ethernet networks. The second interface follows the MII (Media Independent Interface) specification draft standard, consisting of 4 bit wide data transfers at the nibble rate. FEAST also interfaces to the MII serial management protocol. Four I/O ports (one input and three output pins) are provided for LAN83C694 configuration.

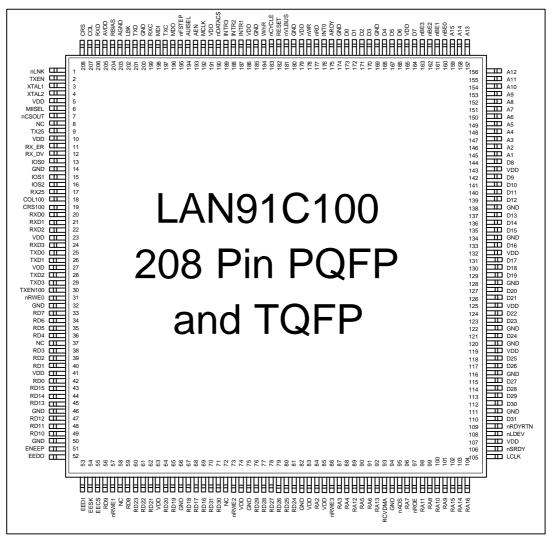

#### **PIN CONFIGURATION**

| PQFP/TQFP<br>PIN NO.                                                                                                                        | NAME               | SYMBOL    | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 148-159                                                                                                                                     | Address            | A4-A15    | I              | Input. Decoded by the LAN91C100 to determine accesses to its registers.                                                                                                                                                                  |  |  |

| 145-147                                                                                                                                     | Address            | A1-A3     | I              | Input. Used by the LAN91C100 for internal register selection.                                                                                                                                                                            |  |  |

| 193                                                                                                                                         | Address<br>Enable  | AEN       | I              | Input. Used as an address qualifier. Address decoding is only enabled when AEN is low.                                                                                                                                                   |  |  |

| 160-163                                                                                                                                     | nByte<br>Enable    | nBE0-nBE3 | I              | Input. Used during LAN91C100 register accesses to determine the width of the access and the register(s) being accessed. nBE0-nBE3 are ignored when nDATACS is low (burst accesses) because 32 bit transfers are assumed.                 |  |  |

| 173-170,<br>168-166,<br>164,144,<br>142-139,<br>137-135,<br>133,<br>131-129,<br>127,126,<br>124,123,<br>121,118,<br>117,<br>115-112,<br>110 | Data Bus           | D0-D31    | I/O24          | Bidirectional. 32 bit data bus used to access the LAN91C100's internal registers. Data bus has weak internal pullups. Supports direct connection to the system bus without external buffering. For 16 bit systems, only D0-D15 are used. |  |  |

| 182                                                                                                                                         | Reset              | RESET     | IS             | Input. This input is not considered active unless it is active for at least 100ns to filter narrow glitches.                                                                                                                             |  |  |

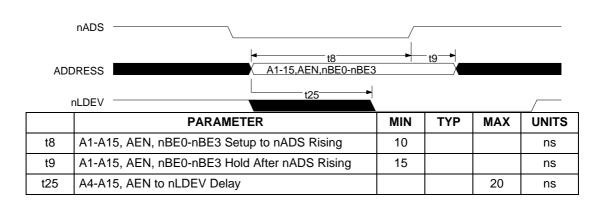

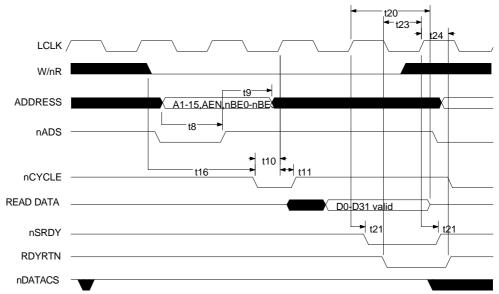

| 95                                                                                                                                          | nAddress<br>Strobe | nADS      | IS             | Input. Address strobe. For systems that require address latching, the rising edge of nADS indicates the latching moment for A1-A15 and AEN. All LAN91C100 internal functions of A1-A15, AEN are latched except for nLDEV decoding.       |  |  |

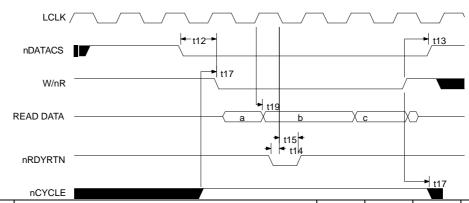

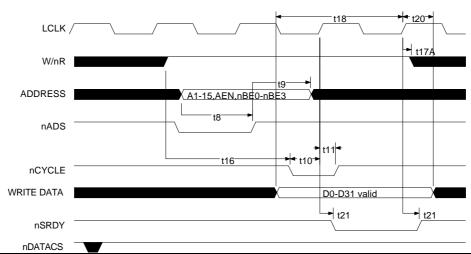

| 183                                                                                                                                         | nCycle             | nCYCLE    | I              | Input. This active low signal is used to control LAN91C100 synchronous bus cycles.                                                                                                                                                       |  |  |

| PQFP/TQFP      |                         |           | BUFFER |                                                                                                                                                                                                                                     |  |

|----------------|-------------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN NO.        | NAME                    | SYMBOL    | TYPE   | DESCRIPTION                                                                                                                                                                                                                         |  |

| 184            | Write/nRea<br>d         | W/nR      | I      | Input. Defines the direction of synchronous cycles. Write cycles when high, read cycles when low.                                                                                                                                   |  |

| 181            | nVL Bus<br>Access       | nVLBUS    | IΡ     | Input. When low the LAN91C100 synchronous bus interface is configured for VL Bus accesses. Otherwise the LAN91C100 is configured for EISA DMA burst accesses. Does not affect the asynchronous bus interface.                       |  |

| 105            | Local Bus<br>Clock      | LCLK      | I      | Input. Used to interface synchronous buses. Maximum frequency is 50 MHz. Limited to 8.33 MHz for EISA DMA burst mode.                                                                                                               |  |

| 175            | Asynchron-<br>ous Ready | ARDY      | OD16   | Open drain output. ARDY may be used when interfacing asynchronous buses to extend accesses. Its rising (access completion) edge is controlled by the XTAL1 clock and therefore asynchronous to the host CPU or bus clock.           |  |

| 106            | nSynchron-<br>ous Ready | nSRDY     | O16    | Output. This output is used when interfacing synchronous buses and nVLBUS=0 to extend accesses. This signal remains normally inactive, and its falling edge indicates completion. This signal is synchronous to the bus clock LCLK. |  |

| 109            | nReady<br>Return        | nRDYRTN   | I      | Input. This input is used to complete synchronous read cycles. In EISA burst mode it is sampled on falling LCLK edges, and synchronous cycles are delayed until it is sampled high.                                                 |  |

| 176<br>187-189 | Interrupt               | INT0-INT3 | O24    | Outputs. Only one of these interrupts is selected to be used; the other three are tristated. The selection is determined by the value of INT SEL1-0 bits in the Configuration Register.                                             |  |

| PQFP/TQFP |                           |           | BUFFER |                                                                                                                                                                                                                                         |  |

|-----------|---------------------------|-----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PIN NO.   | NAME                      | SYMBOL    | TYPE   | DESCRIPTION                                                                                                                                                                                                                             |  |

| 108       | nLocal<br>Device          | nLDEV     | O16    | Output. This active low output is asserted when AEN is low and A4-A15 decode to the LAN91C100 address programmed into the high byte of the Base Address Register. nLDEV is a combinatorial decode of unlatched address and AEN signals. |  |

| 177       | nRead<br>Strobe           | nRD       | IS     | Input. Used in asynchronous bus interfaces.                                                                                                                                                                                             |  |

| 178       | nWrite<br>Strobe          | nWR       | IS     | Input. Used in asynchronous bus interfaces.                                                                                                                                                                                             |  |

| 190       | nData Path<br>Chip Select | nDATACS   | IP     | Input. When nDATACS is low, the Dat Path can be accessed regardless of the values of AEN, A1-A15 and the content of the BANK SELECT Register. nDATAC provides an interface for bursting to an from the LAN91C100 32 bits at a time.     |  |

| 54        | EEPROM<br>Clock           | EESK      | O4     | Output. 4 $\mu sec$ clock used to shift data in and out of the serial EEPROM.                                                                                                                                                           |  |

| 55        | EEPROM<br>Select          | EECS      | O4     | Output. Used for selection and command framing of the serial EEPROM.                                                                                                                                                                    |  |

| 52        | EEPROM<br>Data Out        | EEDO      | O4     | Output. Connected to the DI input of the serial EEPROM.                                                                                                                                                                                 |  |

| 53        | EEPROM<br>Data In         | EEDI      | ID     | Input. Connected to the DO output of the serial EEPROM.                                                                                                                                                                                 |  |

| 13,15,16  | I/O Base                  | IOS0-IOS2 | IP     | Input. External switches can be connecte to these lines to select between predefine EEPROM configurations.                                                                                                                              |  |

| 51        | Enable<br>EEPROM          | ENEEP     | IP     | Input. Enables (when high or open) LAN91C100 accesses to the serial EEPROM. Must be grounded if no EEPROM is connected to the LAN91C100.                                                                                                |  |

| DESCRIPTION OF                                                                                |                        |                | 1      |                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------|------------------------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PQFP/TQFP                                                                                     | PQFP/TQFP              |                | BUFFER |                                                                                                                                                               |

| PIN NO.                                                                                       | NAME                   | SYMBOL         | TYPE   | DESCRIPTION                                                                                                                                                   |

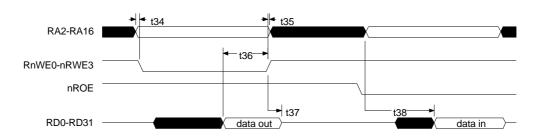

| 42,<br>40-38,<br>36-33, 59,56,<br>49-47,<br>45-43,<br>69-67, 65,64,<br>62-60,<br>81-76, 71,70 | RAM Data<br>Bus        | RD0-RD31       | I/O4P  | Bidirectional. Carries the local buffer memory read and write data. Reads are always 32 bits wide. Writes are controlled individually at the byte level.      |

| 84,87,<br>88,90,<br>91,96,<br>99,101,<br>100,98,<br>89,92,<br>103,102,<br>104                 | RAM<br>Address<br>Bus  | RA2-RA16       | O4     | Outputs. This bus specifies the buffer RAM doubleword being accessed by the LAN91C100.                                                                        |

| 97                                                                                            |                        | nROE           | O4     | Output. Used to read a doubleword from buffer RAM.                                                                                                            |

| 31,57,<br>73,86                                                                               |                        | nRWE0-<br>RWE3 | O4     | Outputs. Used to write any byte, word or dword in RAM.                                                                                                        |

| 93                                                                                            | nReceive<br>DMA        | nRCVDMA        | O4     | Output. This pin is active during LAN91C100 write memory cycles of receive packets.                                                                           |

| 3<br>4                                                                                        | Crystal 1<br>Crystal 2 | XTAL1<br>XTAL2 | Iclk   | An external 25 MHz crystal is connected across these pins. If a TTL clock is supplied instead, it should be connected to XTAL1 and XTAL2 should be left open. |

| 5,10,<br>23,27,<br>41,63,<br>74,83,<br>85,107,<br>119,125,<br>132,143,<br>165,179,<br>186,191 | Power                  | VDD            |        | +5V power supply pins.                                                                                                                                        |

| 205                                                                                           | Analog<br>Power        | AVDD           |        | +5V analog power supply pin.                                                                                                                                  |

| PQFP/TQFP BUFFER                |                        |        |      |                                                                                                              |  |

|---------------------------------|------------------------|--------|------|--------------------------------------------------------------------------------------------------------------|--|

| PIN NO.                         | NAME                   | SYMBOL | TYPE | DESCRIPTION                                                                                                  |  |

| 14,32,<br>46,50,                | Ground                 | GND    |      | Ground pins.                                                                                                 |  |

| 66,75,<br>82,94,<br>111,116,    |                        |        |      |                                                                                                              |  |

| 120,122,<br>128,134,            |                        |        |      |                                                                                                              |  |

| 138,169,<br>174,180,<br>185,200 |                        |        |      |                                                                                                              |  |

| 203                             | Analog<br>Ground       | AGND   |      | Analog ground pin.                                                                                           |  |

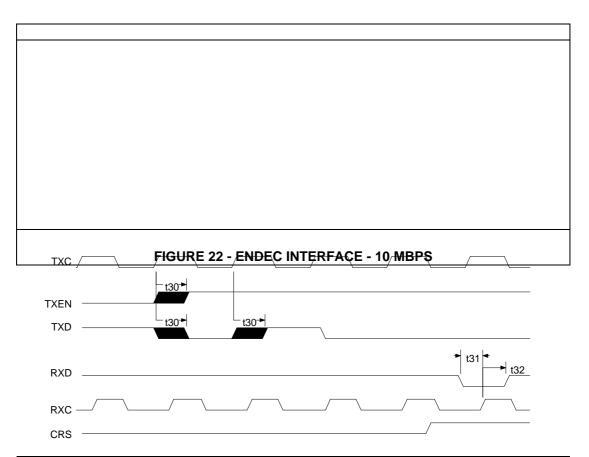

| 2                               | Transmit<br>Enable     | TXEN   | 04   | Output. Used for 10 Mbps ENDEC. This pin stays low when MIISEL is high.                                      |  |

| 201                             | Transmit<br>Data       | TXD    | O4   | NRZ transmit data output for 10 Mbps ENDEC interface.                                                        |  |

| 208                             | Carrier<br>Sense       | CRS    | ID   | Input. Carrier sense from 10 Mbps ENDE interface. This pin is ignored when MISE is high.                     |  |

| 207                             | Collision<br>Detection | COL    | ID   | Input. Collision detection indication from 10 Mbps ENDEC interface. This pin is ignored when MIISEL is high. |  |

| 206                             | Receive<br>Data        | RXD    | IP   | NRZ receive data input from 10 Mbps ENDEC interface. This pin is ignored when MIISEL is high.                |  |

| 197                             | Transmit<br>Clock      | TXC    | IP   | Input. 10 MHz transmit clock used in 10 Mbps operation. This pin is ignored when MIISEL is high.             |  |

| 199                             | Receive<br>Clock       | RXC    | IP   | Input. 10Mhz receive clock recovered by the 10 Mbps ENDEC. This pin is ignored when MIISEL is high.          |  |

| 202                             | Loopback               | LBK    | O4   | Output. Active when LOOP bit is set (TCR bit 1). Independent of port selection (MIISEL=X).                   |  |

| PQFP/TQFP       |                                 |               | BUFFER |                                                                                                                                                              |

|-----------------|---------------------------------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.         | NAME                            | SYMBOL        | TYPE   | DESCRIPTION                                                                                                                                                  |

| 1               | nLink Status                    | nLNK          | IP     | Input. General purpose input port used to convey LINK status (EPHSR bit 14). Independent of port selection (MIISEL=X).                                       |

| 195             | nFullstep                       | nFSTEP        | O4     | Output. Non volatile output pin. Driven by inverse of FULLSTEP (CONFIG bit 10). Independent of port selection (MII SEL=X).                                   |

| 6               | MII Select                      | MIISEL        | O4     | Output. Non volatile output pin. Driven by MII SELECT (CONFIG bit 15). High indicates the MII port is selected, low indicates the 10 Mbps ENDEC is selected. |

| 194             | AUI Select                      | AUISEL        | O4     | Output. Non volatile output pin. Driven by AUI SELECT (CONFIG bit 8). Independent of port selection (MIISEL=X).                                              |

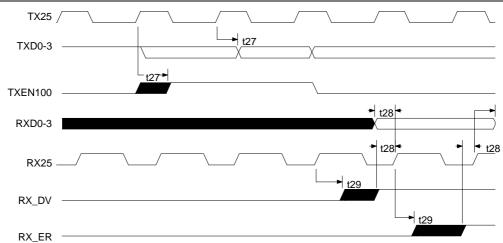

| 30              | Transmit<br>Enable 100<br>Mbps  | TXEN100       | O4     | Output to MII PHY. Envelope to 100 Mbps transmission. This pin stays low if MIISEL is low.                                                                   |

| 19              | Carrier 100<br>Mbps             | CRS100        | IP     | Input from MII PHY. Envelope of packet reception used for deferral and backoff purposes. This pin is ignored when MIISEL is low.                             |

| 12              | Receive<br>Data Valid           | RX_DV         | ID     | Input from MII PHY. Envelope of data valid reception. Used for receive data framing. This pin is ignored when MIISEL is low.                                 |

| 18              | Collision<br>Detect 100<br>Mbps | COL100        | ID     | Input from MII PHY. Collision detection input. This pin is ignored when MIISEL is low.                                                                       |

| 25,26,<br>28,29 | Transmit<br>Data                | TXD0-TXD3     | O4     | Outputs. Transmit Data nibble to MII PHY.                                                                                                                    |

| 9               | Transmit<br>Clock               | TX25          | IP     | Input. Transmit clock input from MII. Nibble rate clock (25 MHz). This pin is ignored when MIISEL is low.                                                    |

| 17              | Receive<br>Clock                | RX25          | IP     | Input. Receive clock input from MII PHY. Nibble rate clock. This pin is ignored when MIISEL is low.                                                          |

| 20,21,<br>22,24 | Receive<br>Data                 | RXD0-<br>RXD3 | l      | Inputs. Received Data nibble from MII PHY. These pins are ignored when MIISEL is low.                                                                        |

| PQFP/TQFP |                                |        | BUFFER          |                                                                                                                                                                                                                                                        |

|-----------|--------------------------------|--------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NO.   | NAME                           | SYMBOL | TYPE            | DESCRIPTION                                                                                                                                                                                                                                            |

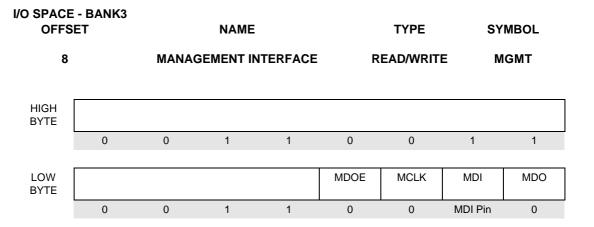

| 198       | Manage-<br>ment Data<br>Input  | MDI    | IP              | MII management data input.                                                                                                                                                                                                                             |

| 196       | Manage-<br>ment Data<br>Output | MDO    | O4              | MII management data output.                                                                                                                                                                                                                            |

| 192       | Manage-<br>ment Clock          | MCLK   | O4              | MII management clock.                                                                                                                                                                                                                                  |

| 11        | Receive<br>Error               | RX_ER  | ID              | Input. Indicates a code error detected by PHY. Used by the LAN91C100 to discard the packet being received. The error indication reported for this event is the same as a bad CRC (Receive Status Word bit 13). This pin is ignored when MIISEL is low. |

| 204       | Bias<br>Resistor               | RBIAS  | Analog<br>Input | A bias resistor is connected between this pin and ground. Nominal value is TBD.                                                                                                                                                                        |

| 7         | nChip<br>Select<br>Output      | nCSOUT | O4              | Output. Chip Select provided for mapping of PHY functions into LAN91C100 decoded space. Active on accesses to LAN91C100's eight lower addresses when the BANK SELECTED is 7.                                                                           |

Table 1 - LAN91C100 Pin Requirements

| FUNCTION                    | PIN SYMBOLS                                                                                        | NUMBER OF PINS |

|-----------------------------|----------------------------------------------------------------------------------------------------|----------------|

| System Address Bus          | A1-A15, AEN, nBE0-nBE3                                                                             | 20             |

| System Data Bus             | D0-D31                                                                                             | 32             |

| System Control Bus          | RESET, nADS, LCLK, ARDY, nRDYRTN, nSRDY, INT0-INT3, nLDEV, nRD, nWR, nDATACS, nCYCLE, W/nR, nVLBUS | 17             |

| Serial EEPROM               | EEDI, EEDO, EECS, EESK, ENEEP, IOS0-IOS2                                                           | 8              |

| RAM Data Bus                | RD0-RD31                                                                                           | 32             |

| RAM Address Bus             | RA2-RA16                                                                                           | 15             |

| RAM Control Bus             | nROE, nRWE0-nRWE3, RCVDMA                                                                          | 6              |

| Crystal Oscillator          | XTAL1, XTAL2                                                                                       | 2              |

| Power                       | VDD, AVDD                                                                                          | 19             |

| Ground                      | GND, AGND                                                                                          | 21             |

| External ENDEC 10 Mbps      | TXEN, TXD, CRS, COL, RXD, TXC, RXC, LBK, nLNK, nFSTEP, AUISEL, MIISEL                              | 12             |

| Physical Interface 100 Mbps | TXEN100, CRS100, COL100, RX_DV,<br>RX_ER, TXD0-TXD3, RXD0-RXD3, MDI,<br>MDO, MCLK                  | 16             |

| Clocks                      | TX25, RX25                                                                                         | 2              |

| Miscellaneous               | RBIAS, nCSOUT                                                                                      | 2              |

| TOTAL                       |                                                                                                    | 204            |

FIGURE 2 - LAN91C100 FEAST SYSTEM DIAGRAM

#### **FUNCTIONAL DESCRIPTION**

#### **DESCRIPTION OF BLOCKS**

#### **Clock Generator Block**

The LAN91C100's clock generator uses a 25 MHz crystal connected to pins XTAL1 XTAL2 and generates two free running clocks:

- 50 MHz free running clock Supplied to the DMA and the ARBITER blocks.

- 25 MHz free running clock Used to run the EPH during reset or when no TX25 is present.

#### Other clocks:

- TXCLK and RXCLK are 10 MHz clock inputs. These clocks are generated by the external ENDEC in 10 Mbps mode and are only used by the CSMA/CD block.

- 4) TX25 is an input clock. It will be the nibble rate of the particular PHY connected to the MII (2.5 MHz for a 10 Mbps PHY, and 25 MHz for a 100 Mbps PHY).

- 5) RX25 This is the MII nibble rate receive clock used for sampling received data nibbles and running the receive state machine (2.5 MHz for a 10 Mbps PHY, and 25 MHz for a 100 Mbps PHY).

- LCLK Bus clock Used by the BIU for synchronous accesses. Maximum frequency is 50 MHz for VL BUS mode, and 8.5 MHz for EISA slave DMA.

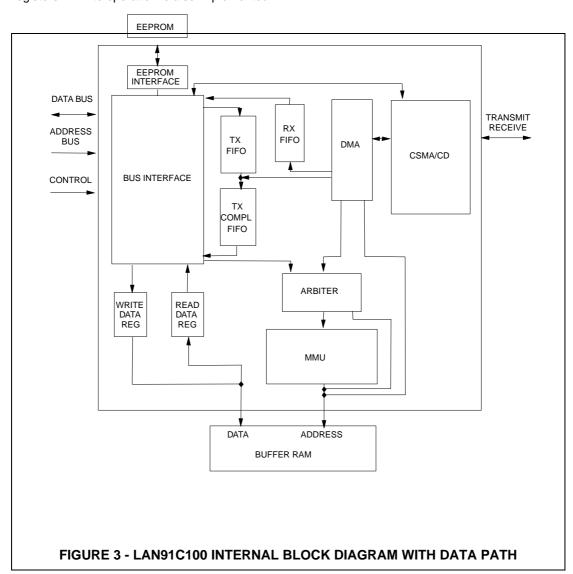

#### **CSMA/CD Block**

This is a 16-bit oriented block, with fully-independent Transmit and Receive logic. The data path in and out of the block consists of two 6-bit wide uni-directional FIFOs interfacing the

DMA block. The DMA port of the FIFO stores 32 bits exploiting the 32-bit data path into memory. The Control Path consists of a set of registers interfaced to the CPU via the BIU.

#### **DMA Block**

This block accesses packet memory on the CSMA/CD's behalf, fetching transmit data and storing received data. It interfaces the CSMA/CD Transmit and Receive FIFOs on one side, and the Arbiter block on the other. The data path is 32 bits wide.

The DMA machine is able to support full duplex operation. Independent receive and transmit counters are used. Transmit and receive cycles are alternated when simultaneous receive and transmit accesses are needed.

#### **Arbiter Block**

The Arbiter block sequences accesses to packet RAM requested by the BIU and by the DMA blocks. BIU requests represent pipelined CPU accesses to the Data Register, while DMA requests represent CSMA/CD data movement. The external memory devices used are 25ns 32kx8 SRAM. The cycle time for CPU consecutive accesses to the Data Path is 80ns/doubleword. This time includes arbitration and CSMA memory cycles.

The Arbiter is also responsible for controlling the nRWE0-nRWE3 lines as a function of the bytes being written. Read accesses are always 32 bits wide, and the Arbiter steers the appropriate byte(s) to the appropriate lanes as a function of the address.

The CPU Data Path consists of two unidirectional FIFOs mapped at the Data Register location. These FIFOs can be accessed in any combination of bytes, word, or doublewords. The Arbiter will indicate 'Not Ready' whenever a cycle is initiated that cannot be satisfied by the present state of the FIFO.

The depth of the FIFOs will accommodate the worst case arbitration and byte access alignment pattern while still preserving the CPU cycle time when accessing the Data Register.

#### **MMU Block**

The Hardware Memory Management Unit is similar to the LAN91C90's MMU. It does dynamic memory allocation and queuing of transmit and receive packets, and it determines the value of the transmit and receive interrupts as a function of the queues. The page size is still 2k, and with a maximum memory size of 128k the MMU uses 64x6 FIFOs. MIR and MCR values are interpreted in 512 byte units.

#### **BIU Block**

The Bus Interface Unit can handle synchronous as well as asynchronous buses; different signals are used for each one. Transparent latches are added on the address path using rising nADS for latching.

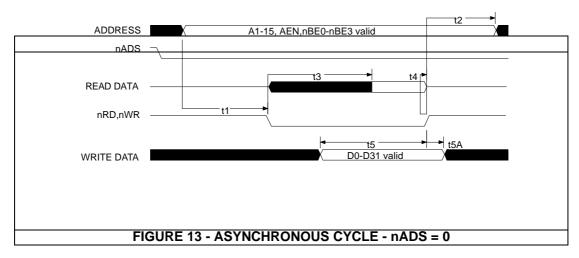

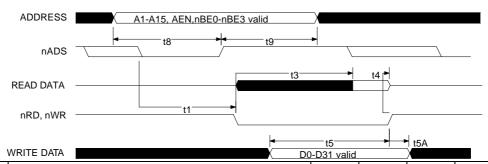

When working with an asynchronous bus like ISA, the read and write operations are controlled by the edges of nRD and nWR. ARDY is used for notifying the system that it should extend the access cycle. The leading edge of ARDY is generated by the leading edge of nRD or nWR while the trailing edge of ARDY is controlled by the LAN91C100's internal clock and, therefore, is asynchronous to the bus.

In the synchronous VL Bus type mode, nCYCLE and LCLK are used for read and write operations. Completion of the cycle may be

determined by using nSRDY. nSRDY is controlled by LCLK and is synchronous to the bus

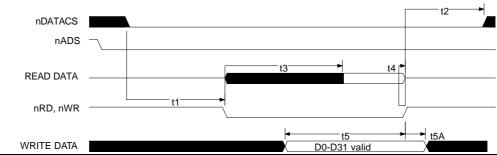

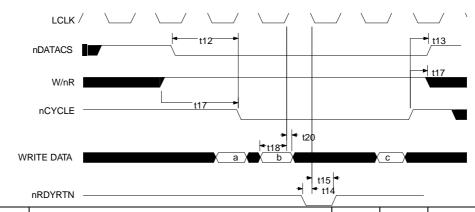

Direct 32-bit access to the Data Path is supported by using the nDATACS input. By asserting nDATACS, external DMA-type of devices will bypass the BIU address decoders and can sequentially access memory with no CPU intervention. nDATACS accesses can be used in the DMA burst mode (nVLBUS=1) or in asynchronous cycles. These cycles MUST be 32-bit cycles. Please refer to the corresponding timing diagrams for details on these cycles.

#### **MAC-PHY Interface**

Two separate interfaces are defined; one for the 10 Mbps bit rate interface and one for the MII 100 Mbps and 10 Mbps nibble rate interface. The 10 Mbps ENDEC interface comprises the signals used for interfacing Ethernet ENDECs. The 100 Mbps interface follows the MII draft standard for 100 Mbps 802.3 networks, and it is based on transferring nibbles between the MAC and the PHY.

For the MII interface, transmit data is clocked out using the TX25 clock input, while receive data is clocked in using RX25.

Switching between the ENDEC and MII interfaces is controlled by the MII Select bit in the Configuration Register. The MIISEL pin reflects the value of the bit and may be used to control external multiplexing logic.

#### **MII Management Interface Block**

PHY management through the MII management interface is supported by the LAN91C100 by providing the means to drive a tri-statable data output, a clock, and reading an input. Timing and framing for each management command is be generated by the CPU.

#### **Serial EEPROM Interface Block**

This block is responsible for reading the serial EEPROM upon hardware reset (or equivalent command) and defining defaults for some key registers. A write operation is also implemented

by this block which, under CPU command, will program specific locations in the EEPROM. This block is an autonomous state machine, and it controls the LAN91C100's internal Data Bus during active operation.

#### **DATA STRUCTURES AND REGISTERS**

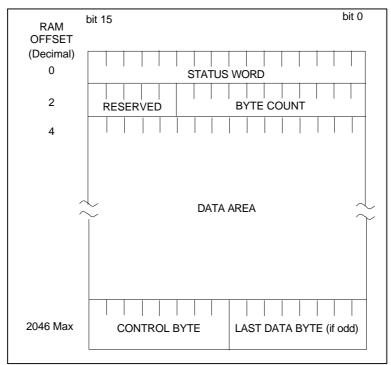

#### PACKET FORMAT IN BUFFER MEMORY

The packet format in memory is similar for the Transmit and Receive areas. The first word is

reserved for the status word, the next word is used to specify the total number of bytes, and it is followed by the data area. The data area holds the packet itself.

FIGURE 4 - DATA PACKET FORMAT

|              | TRANSMIT PACKET                                                | RECEIVE PACKET                                                     |

|--------------|----------------------------------------------------------------|--------------------------------------------------------------------|

| STATUS WORD  | Written by CSMA upon transmit completion (see Status Register) | Written by CSMA upon receive completion (see RX Frame Status Word) |

| BYTE COUNT   | Written by CPU                                                 | Written by CSMA                                                    |

| DATA AREA    | Written/modified by CPU                                        | Written by CSMA                                                    |

| CONTROL BYTE | Written by CPU to control odd/even data bytes                  | Written by CSMA; also has odd/even bit                             |

BYTE COUNT - Divided by two, it defines the total number of words, including the STATUS WORD, the BYTE COUNT WORD, the DATA AREA and the CONTROL BYTE.

The receive byte count always appears as even, the ODDFRM bit of the receive status word indicates if the low byte of the last word is relevant.

The transmit byte count least significant bit will be assumed 0 by the controller regardless of the value written in memory.

DATA AREA - The data area starts at offset 4 of the packet structure, and it can extend for up to 2043 bytes.

The data area contains six bytes of DESTINATION ADDRESS followed by six bytes of SOURCE ADDRESS, followed by a variable length number of bytes. On transmit, all bytes are provided by the CPU, including the source address. The LAN91C100 does not insert its own source address. On receive, all bytes are provided by the CSMA side.

The 802.3 Frame Length word (Frame Type in Ethernet) is not interpreted by the LAN91C100. It is treated transparently as data both for transmit and receive operations.

CONTROL BYTE - For transmit packets the CONTROL BYTE is written by the CPU as:

| Х | Х | ODD | CRC | 0 | 0 | 0 | 0 |

|---|---|-----|-----|---|---|---|---|

|   |   |     |     |   |   |   |   |

ODD If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the number of data bytes is even and the byte before the CONTROL BYTE is not transmitted.

CRC When set, CRC will be appended to the frame. This bit has only meaning if the NOCRC bit in the TCR is set.

For receive packets the CONTROL BYTE is written by the controller as:

|  |  | 0 | 1 | ODD | 0 | 0 | 0 | 0 | 0 |

|--|--|---|---|-----|---|---|---|---|---|

|--|--|---|---|-----|---|---|---|---|---|

ODD If set, indicates an odd number of bytes, with the last byte being right before the CONTROL BYTE. If clear, the number of data

bytes is even and the byte before the CONTROL BYTE should be ignored.

#### **RECEIVE FRAME STATUS WORD**

This word is written at the beginning of each receive frame in memory. It is not available as a register.

| ERR | CAST | CRC | FRM  | TOOLNG | TOO<br>SHORT       |   |              |

|-----|------|-----|------|--------|--------------------|---|--------------|

|     |      |     | HASH | VALUE  |                    |   | MULT<br>CAST |

|     | 5    | 4   | 3    | 2      | 1                  | 0 |              |

|     |      | 5   | 5 4  |        | HASH VALUE 5 4 3 2 |   |              |

ALGNERR Frame had alignment error. When MII SEL=1 alignment error is set when BADCRC=1 and an odd number of nibbles were received between SFD and RX\_DV going inactive. When MII SEL=0 alignment error is set when BADCRC=1 and the number of bits received between SFD and the CRS going inactive is not an octet multiple.

BRODCAST Receive frame was broadcast.

BADCRC Frame had CRC error, or RX\_ER was asserted during reception.

ODDFRM This bit, when set, indicates that the received frame had an odd number of bytes.

TOOLNG Frame length was longer than 802.3 maximum size (1518 bytes on the cable).

TOOSHORT Frame length was shorter than 802.3 minimum size (64 bytes on the cable).

HASH VALUE Provides the hash value used to index the Multicast Registers. Can be used by receive routines to speed up the group address search. The hash value consists of the six most significant bits of the CRC calculated on the Destination Address, and maps into the 64 bit multicast table. Bits 5,4,3 of the hash value select a byte of the multicast table, while bits 2,1,0 determine the bit within the byte selected. Examples of the address mapping:

| ADDRESS           | HASH VALUE 5-0 | MULTICAST TABLE BIT |

|-------------------|----------------|---------------------|

| ED 00 00 00 00 00 | 000 000        | MT-0 bit 0          |

| 0D 00 00 00 00 00 | 010 000        | MT-2 bit 0          |

| 01 00 00 00 00 00 | 100 111        | MT-4 bit 7          |

| 2f 00 00 00 00 00 | 111 111        | MT-7 bit 7          |

MULTCAST Receive frame was multicast. If hash value corresponds to a multicast table bit that is set, and the address was a multicast,

the packet will pass address filtering regardless of other filtering criteria.

#### I/O SPACE

The base I/O space is determined by the IOS0-2 inputs and the EEPROM contents. To limit the I/O space requirements to 16 locations, the registers are assigned to different banks. The

last word of the I/O area is shared by all banks and can be used to change the bank in use. Registers are described using the following convention:

|              | OFFSI  | ΕT    | NAME   |        | TYPE   | SY     | MBOL  |       |

|--------------|--------|-------|--------|--------|--------|--------|-------|-------|

| HIGH<br>BYTE | bit 15 | bit14 | bit 13 | bit 12 | bit 11 | bit 10 | bit9  | bit8  |

|              | Х      | Х     | Χ      | Χ      | Х      | Х      | Х     | Χ     |

| LOW<br>BYTE  | bit 7  | bit 6 | bit 5  | bit 4  | bit 3  | bit 2  | bit 1 | bit 0 |

|              | Х      | Х     | Х      | Х      | Х      | Х      | Х     | Х     |

OFFSET Defines the address offset within the IOBASE where the register can be accessed at, provided the bank select has the appropriate value.

The offset specifies the address of the even byte (bits 0-7) or the address of the complete word.

The odd byte can be accessed using address (offset + 1).

Some registers (like the Interrupt Ack., or like Interrupt Mask) are functionally described as two eight bit registers, in that case the offset of each one is independently specified.

Regardless of the functional description, all registers can be accessed as doublewords, words or bytes.

The default bit values upon hard reset are highlighted below each register.

Table 2 - Internal I/O Space Mapping

|   | BANK0        | BANK1              | BANK2       | BANK3       |

|---|--------------|--------------------|-------------|-------------|

| 0 | TCR          | CONFIG             | MMU COMMAND | MT0-1       |

| 2 | EPH STATUS   | BASE               | PNR/ARR     | MT2-3       |

| 4 | RCR          | IA0-1              | FIFO PORTS  | MT4-5       |

| 6 | COUNTER      | IA2-3              | POINTER     | MT6-7       |

| 8 | MIR          | IA4-5              | DATA        | MGMT        |

| Α | MCR          | GENERAL<br>PURPOSE | DATA        | REVISION    |

| С | RESERVED (0) | CONTROL            | INTERRUPT   | ERCV        |

| Е | BANK SELECT  | BANK SELECT        | BANK SELECT | BANK SELECT |

A special BANK (BANK7) exists to support the addition of external registers.

#### **BANK SELECT REGISTER**

| OFFSET       |   |      | NAME                 |   |   | TYPE           | SY  | MBOL |  |

|--------------|---|------|----------------------|---|---|----------------|-----|------|--|

| E            |   | BANK | BANK SELECT REGISTER |   |   | READ/WRITE BSR |     |      |  |

| HIGH<br>BYTE | 0 | 0    | 1                    | 1 | 0 | 0              | 1   | 1    |  |

|              | 0 | 0    | 1                    | 1 | 0 | 0              | 1   | 1    |  |

| LOW<br>BYTE  |   |      |                      |   |   | BS2            | BS1 | BS0  |  |

|              | Χ | Χ    | Χ                    | Χ | Χ | 0              | 0   | 0    |  |

BS2, BS1, BS0 Determine the bank presently in use. This register is always accessible and is used to select the register bank in use.

The upper byte always reads as 33h and can be used to help determine the I/O location of FEAST.

The BANK SELECT REGISTER is always accessible regardless of the value of BS0-2.

Note that the bank select register can be accessed as a doubleword at offset Ch, as a word at offset Eh, or as at offset Fh, however

a doubleword write to offset Ch will write the BANK SELECT REGISTER but will not write the registers Ch and Dh.

BANK 7 has no internal registers other than the BANK SELECT REGISTER itself. On valid cycles where BANK7 is selected (BS0=BS1=BS2=1), and A3=0, nCSOUT is activated to facilitate implementation of external registers.

Note: BANK7 does not exist in LAN91C9x devices. For backward S/W compatibility BANK7 accesses should be done if the Revision Control register indicates the device is LAN91C100.

OFFSET NAME TYPE SYMBOL

O TRANSMIT CONTROL REGISTER READ/WRITE TCR

This register holds bits programmed by the CPU to control some of the protocol transmit options.

| HIGH<br>BYTE |        |   | EPH<br>LOOP | STP<br>SQET | FDUPLX | MON_<br>CSN |      | NOCRC |

|--------------|--------|---|-------------|-------------|--------|-------------|------|-------|

|              | Х      | Х | 0           | 0           | 0      | 0           | Х    | 0     |

|              |        |   |             |             |        |             |      |       |

| LOW          | PAD_EN |   |             |             |        | FORCOL      | LOOP | TXENA |

| BYTE         |        |   |             |             |        |             |      |       |

|              | 0      | Χ | Χ           | Χ           | Χ      | 0           | 0    | 0     |

EPH\_LOOP Internal loopback at the EPH block. Serial data is looped back when set. Defaults low. When EPH\_LOOP is high, the following transmit outputs are forced inactive: TXD0-3=0h, TXEN100=TXEN=0, TXD=1. The following external inputs are blocked: CRS=CRS100=0, COL=COL100=0, RX\_DV=RX\_ER=0.

STP\_SQET Stop transmission on SQET error. If set, stops and disables transmitter on SQE test error. Does not stop on SQET error and transmits next frame if clear. Defaults low.

FDUPLX When set it enables full duplex operation. This will cause frames to be received if they pass the address filter regardless of the source for the frame. When clear the node will not receive a frame sourced by itself.

MON\_CSN When set, the LAN91C100 monitors carrier while transmitting. It must see its own carrier by the end of the preamble. If it is not seen, or if carrier is lost during transmission, the transmitter aborts the frame

without CRC and turns itself off. When this bit is clear the transmitter ignores its own carrier. Defaults low.

NOCRC Does not append CRC to transmitted frames when set; allows software to insert the desired CRC. Defaults to 0 (CRC inserted).

PAD\_EN When set, the LAN91C100 will pad transmit frames shorter than 64 bytes with 00. Does not pad frames when reset.

FORCOL When set, the transmitter will force a collision by not deferring deliberately. After the collision this bit is reset automatically. This bit defaults low to normal operation.

LOOP Loopback. General purpose output port used to control the LBK pin. Typically used to put the PHY chip in loopback mode.

TXENA Transmit enabled when set. Transmit is disabled if clear. When the bit is cleared, the LAN91C100 will complete the current transmission before stopping. When stopping due to an error, this bit is automatically cleared.

#### I/O SPACE - BANK 0

OFFSET NAME TYPE SYMBOL

#### 2 EPH STATUS REGISTER READ ONLY EPHSR

This register stores the status of the last frame transmitted. This register value, upon individual transmit packet completion, is stored as the first word in the memory area allocated to the packet. Packet interrupt processing should use the copy in memory as the register itself will be updated by subsequent packet transmissions. The register can be used for real time values (like TXENA and LINK OK). If TXENA is cleared the register holds the last packet completion status.

| HIGH<br>BYTE | TX UNRN | LINK_OK   | RX_OVRN | CTR_ROL | EXC_DEF  | LOST<br>CARR | LATCOL      |        |

|--------------|---------|-----------|---------|---------|----------|--------------|-------------|--------|

|              | 0       | -nLNK Pin | 0       | 0       | 0        | 0            | 0           | Χ      |

|              |         |           |         |         |          |              |             |        |

| LOW<br>BYTE  | TX DEFR | LTX BRD   | SQET    | 16COL   | LTX MULT | MUL COL      | SNGL<br>COL | TX_SUC |

|              | 0       | 0         | 0       | 0       | 0        | 0            | 0           | 0      |

TXUNRN Transmit Under Run. Set if under run occurs, it also clears TXENA bit in TCR. Cleared by setting TXENA high. This bit should never be set under normal operation.

LINK\_OK General purpose input port driven by nLNK pin inverted. Typically used for LINK Test. A transition on the value of this bit generates an interrupt.

RX\_OVRN Upon FIFO overrun, the receiver asserts this bit and clears the FIFO. The receiver stays enabled. After a valid preamble has been detected on a subsequent frame, RX\_OVRN is de-asserted. The RX\_OVRN INT bit in the Interrupt Status Register will also be set and stay set until cleared by the CPU. Note that receive overruns could occur only if receive memory allocations fail.

CTR\_ROL Counter Roll Over. When set, one or more 4-bit counters have reached maximum count (15). Cleared by reading the ECR register.

EXC\_DEF Excessive Deferral. When set last/current transmit was deferred for more than 1518 \* 2 byte times. Cleared at the end of every packet sent.

LOST\_CARR Lost Carrier Sense. When set, indicates that Carrier Sense was not present at end of preamble. Valid only if MON\_CSN is enabled. This condition causes TXENA bit in TCR to be reset. Cleared by setting TXENA bit in TCR.

LATCOL Late collision detected on last transmit frame. If set, a late collision was detected (later than 64 byte times into the frame). When detected, the transmitter JAMs and turns itself off, clearing the TXENA bit in TCR. Cleared by setting TXENA in TCR.

TX\_DEFR Transmit Deferred. When set, carrier was detected during the first 6.4  $\mu sec$  of the inter frame gap. Cleared at the end of every packet sent.

LTX BRD Last transmit frame was a broadcast.

Set if frame was broadcast. Cleared at the start of every transmit frame.

SQET Signal Quality Error Test. For 10 Mbps systems, the transmitter opens a 1.6  $\mu s$  window 0.8  $\mu s$  after transmission is completed and the receiver returns inactive. During this window, the transmitter expects to see the SQET signal from the transceiver. The absence of this signal is a 'Signal Quality Error' and is reported in this status bit. Transmission stops and EPH INT is set if STP\_SQET is in the TCR is also set when SQET is set. This bit is cleared by setting TXENA high. The behavior of this bit for 100 Mbps is presently undefined.

16COL 16 collisions reached. Set when 16 collisions are detected for a transmit frame. TXENA bit in TCR is reset. Cleared when TXENA is set high.

LTX\_MULT Last transmit frame was a multicast. Set if frame was a multicast. Cleared at the start of every transmit frame.

MULCOL Multiple collision detected for the last transmit frame. Set when more than one collision was experienced. Cleared when TX\_SUC is high at the end of the packet being sent

SNGLCOL Single collision detected for the last transmit frame. Set when a collision is detected. Cleared when TX\_SUC is high at the end of the packet being sent.

TX\_SUC Last transmit was successful. Set if transmit completes without a fatal error. This bit is cleared by the start of a new frame transmission or when TXENA is set high. Fatal errors are:

16 collisions SQET fail and STP\_SQET = 1 FIFO Underrun Carrier lost and MON\_CSN = 1 Late collision

#### I/O SPACE - BANK 0

| OFFSET       |             |          | NAME    |           |     | TYPE SYMBO     |              |              |

|--------------|-------------|----------|---------|-----------|-----|----------------|--------------|--------------|

| 4            |             | RECEIVE  | CONTROI | L REGISTE | R I | READ/WRITE RCR |              |              |

| HIGH<br>BYTE | SOFT<br>RST | FILT CAR | 0       | 0         | 0   | 0              | STRIP<br>CRC | RXEN         |

|              | 0           | 0        | 0       | 0         | 0   | 0              | 0            | 0            |

| LOW<br>BYTE  |             |          |         |           |     | ALMUL          | PRMS         | RX_<br>ABORT |

|              | 0           | 0        | 0       | 0         | 0   | 0              | 0            | 0            |

SOFT\_RST Software-activated Reset. Active high. Initiated by writing this bit high and terminated by writing the bit low. The LAN91C100's configuration is not preserved except for Configuration, Base, and IA0-5 Registers. EEPROM is not reloaded after software reset.

FILT\_CAR Filter Carrier. When set, filters leading edge of carrier sense for 12 bit times (3 nibble times). Otherwise recognizes a receive frame as soon as carrier sense is active. (Does NOT filter RX\_DV on MII!)

STRIP\_CRC When set, it strips the CRC on received frames. When clear, the CRC is stored in memory following the packet. Defaults low.

RXEN Enables the receiver when set. If cleared, completes receiving current frame and then goes idle. Defaults low on reset.

ALMUL When set, accepts all multicast frames (frames in which the first bit of DA is '1'). When clear accepts only the multicast frames that match the multicast table setting. Defaults low.

PRMS Promiscuous Mode. When set, receives all frames. Does not receive its own transmission unless it is in full duplex!.

RX\_ABORT This bit is set if a receive frame was aborted due to length longer than 2044 bytes. The frame will not be received. The bit is cleared by RESET or by the CPU writing it low.

#### I/O SPACE - BANK 0 OFFSET

NAME

**TYPE**

SYMBOL

6

**COUNTER REGISTER**

READ ONLY

**ECR**

Counts four parameters for MAC statistics. When any counter reaches 15 an interrupt is issued. All counters are cleared when reading the register, and do not wrap around beyond 15.

| HIGH<br>BYTE | NUM | BER OF EXC | . DEFERRE | D TX | NUMBER OF DEFERRED TX |            |            |    |  |

|--------------|-----|------------|-----------|------|-----------------------|------------|------------|----|--|

|              | 0   | 0          | 0         | 0    | 0                     | 0          | 0          | 0  |  |

|              |     |            |           |      |                       |            |            |    |  |

| LOW<br>BYTE  |     |            |           |      |                       | INGLE COLL | ISION COUN | ΙΤ |  |

|              | 0   | 0          | 0         | 0    | 0                     | 0          | 0          | 0  |  |

Each 4-bit counter is incremented every time the corresponding event, as defined in the EPH STATUS REGISTER bit description, occurs. Note that the counters can only increment once per enqueued transmit packet, never faster; limiting the rate of interrupts that can be generated by the counters. For example, if a packet is successfully transmitted after one collision, the SINGLE COLLISION COUNT field is incremented by one. If a packet experiences between two to 16 collisions, the MULTIPLE COLLISION COUNT field is incremented by one.

If a packet experiences deferral, the NUMBER OF DEFERRED TX field is incremented by one, even if the packet experienced multiple deferrals during its collision retries.

The COUNTER REGISTER facilitates maintaining statistics in the AUTO RELEASE mode where no transmit interrupts are generated on successful transmissions.

Reading the register in the transmit service routine will be enough to maintain statistics.

#### I/O SPACE - BANK 0 **SYMBOL OFFSET NAME TYPE MEMORY INFORMATION REGISTER READ ONLY** MIR 8 HIGH FREE MEMORY AVAILABLE (IN BYTES \* 256 \* M) BYTE 1 LOW MEMORY SIZE (IN BYTES \* 256 \* M) BYTE

1

FREE MEMORY AVAILABLE This register can be read at any time to determine the amount of free memory. The register defaults to the MEMORY SIZE upon reset or upon the RESET MMU command.

MEMORY SIZE - This register can be read to determine the total memory size.

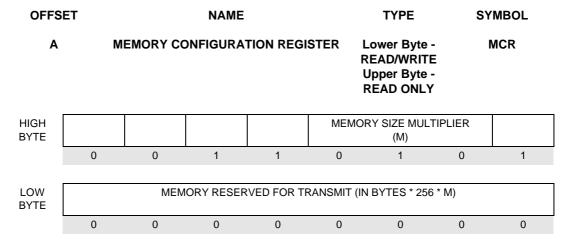

All memory-related information is represented in 256  $^{\star}$  M byte units, where the multiplier M is determined by the MCR upper byte.

These registers default to FFh, which should be interpreted as 256.

#### I/O SPACE - BANK 0

**MEMORY** RESERVED FOR **TRANSMIT** Programming this value allows the host CPU to reserve memory to be used later for transmit, limiting the amount of memory that receive packets can use up. When programmed for zero, the memory allocation between transmit and receive is completely dynamic. programmed for a non-zero value, the allocation is dynamic if the free memory exceeds the programmed value, while receive allocation requests are denied if the free memory is less or equal to the programmed value. This register defaults to zero upon reset. It is not affected by the RESET MMU command.

The value written to the MCR is a reserved memory space IN ADDITION TO ANY MEMORY CURRENTLY IN USE. If the memory allocated for transmit plus the reserved space for transmit is required to be constant (rather than grow with transmit allocations), the CPU should update the value of this register after allocating or releasing memory.

The contents of MIR as well as the low byte of MCR are specified in 256 \* M bytes. The multiplier M is determined by bits 11, 10, and 9 as follows (Bits 11, 10 and 9 are read only bits used by the software driver to transparently run on different controllers of the LAN9000 family):

| DEVICE    | bit 11 | Bit 10 | bit 9 | М  | MAX MEMORY SIZE |

|-----------|--------|--------|-------|----|-----------------|

| LAN91C100 | 0      | 1      | 0     | 2  | 256*256*2=128k  |

| LAN91C90  | 0      | 0      | 1     | 1  | 256*256*1=64k   |

| FUTURE    | 0      | 1      | 1     | 4  | 256k            |

| FUTURE    | 1      | 0      | 0     | 8  | 512k            |

| FUTURE    | 1      | 0      | 1     | 16 | 1M              |

#### I/O SPACE - BANK1 OFFSET

NAME TYPE SYMBOL

0 CONFIGURATION REGISTER READ/WRITE CR

The Configuration Register holds bits that define the adapter configuration and are not expected to change during run-time. This register is part of the EEPROM-saved setup.

| HIGH<br>BYTE | MII<br>SELECT |   |   | NO WAIT  |   | FULL<br>STEP |          | AUI<br>SELECT |

|--------------|---------------|---|---|----------|---|--------------|----------|---------------|

|              | 1             | Х | Χ | 0        | Х | 0            | 0        | 0             |

|              |               |   |   |          |   |              |          |               |

| LOW<br>BYTE  | 1             | 0 |   | RESERVED |   | INT SEL1     | INT SEL0 |               |

|              | 1             | 0 | 1 | 1        | 0 | 0            | 0        | Х             |

MII SELECT Used to select the network interface port. When set, the LAN91C100 will use its MII port and interface a PHY device at the nibble rate. When clear, the LAN91C100 will use its 10 Mbps ENDEC interface. This bit drives the MII SEL pin. Switching between ports should be done with transmitter and receiver disabled and no transmit/receive packets in progress.

NO WAIT When set, does not request additional wait states. An exception to this are accesses to the Data Register if not ready for a transfer. When clear, negates IOCHRDY for two to three clocks on any cycle to the LAN91C100.

FULL STEP This bit is a general purpose output port. Its inverse value drives pin nFSTEP and it is typically connected to SEL pin of the LAN83C694C. It can be used to select the signaling mode for the AUI, or as a general purpose non-volatile configuration pin. Defaults low.

AUI SELECT This bit is a general purpose output port. Its value drives pin AUISEL and it is typically connected to MODE1 pin of the LAN83C694C. It can be used to select AUI vs. 10BASE-T, or as a general purpose non-volatile configuration pin. Defaults low.

INT SEL1-0 Used to select one out of four interrupt pins. The three unused interrupts are tristated.

| INT SEL1 | INT SEL0 | PIN USED |

|----------|----------|----------|

| 0        | 0        | INTR0    |

| 0        | 1        | INTR1    |

| 1        | 0        | INTR2    |

| 1        | 1        | INTR3    |

#### I/O SPACE - BANK1 OFFSET

NAME TYPE SYMBOL

2 BASE ADDRESS REGISTER READ/WRITE BAR

This register holds the I/O address decode option chosen for the LAN91C100. It is part of the EEPROM saved setup, and is not usually modified during run-time.

| HIGH<br>BYTE | A15 | A14 | A13 | A9 | A8 | A7 | A6 | A5 |

|--------------|-----|-----|-----|----|----|----|----|----|

|              | 0   | 0   | 0   | 1  | 1  | 0  | 0  | 0  |

|              |     |     |     |    |    |    |    |    |

| LOW<br>BYTE  |     |     |     |    |    |    |    |    |

|              | 0   | 0   | 0   | 0  | 0  | 0  | 0  | Х  |

A15-A13 and A9-A5 These bits are compared against the I/O address on the bus to determine the IOBASE for the LAN91C100's registers. The 64k I/O space is fully decoded by the LAN91C100 down to a 16 location space,

therefore, the unspecified address lines A4, A10, A11 and A12 must be all zeros.

All bits in this register are loaded from the serial EEPROM. The I/O base decode defaults to 300h (namely, the high byte defaults to 18h).

#### I/O SPACE - BANK1 OFFSET

NAME

**TYPE**

**SYMBOL**

4 THROUGH 9

**INDIVIDUAL ADDRESS REGISTERS**

READ/WRITE

IAR

These registers are loaded starting at word location 20h of the EEPROM upon hardware reset or EEPROM reload. The registers can be modified by the software driver, but a STORE operation will not modify the EEPROM Individual Address contents. Bit 0 of Individual Address 0 register corresponds to the first bit of the address on the cable.

| HIGH<br>BYTE | ADDRESS 0 |   |   |   |   |   |   |   |  |

|--------------|-----------|---|---|---|---|---|---|---|--|

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| LOW<br>BYTE  | ADDRESS 1 |   |   |   |   |   |   |   |  |

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| HIGH<br>BYTE | ADDRESS 2 |   |   |   |   |   |   |   |  |

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| LOW<br>BYTE  | ADDRESS 3 |   |   |   |   |   |   |   |  |

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| HIGH<br>BYTE | ADDRESS 4 |   |   |   |   |   |   |   |  |

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

| LOW<br>BYTE  | ADDRESS 5 |   |   |   |   |   |   |   |  |

|              | 0         | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

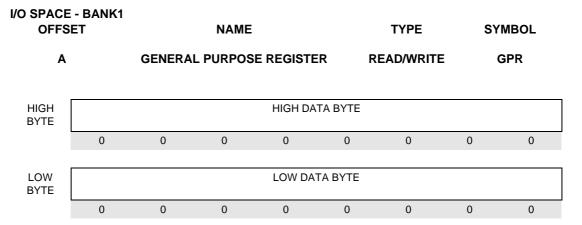

This register can be used as a way of storing and retrieving non-volatile information in the EEPROM to be used by the software driver. The storage is word oriented, and the EEPROM word address to be read or written is specified using the six lowest bits of the Pointer Register.

This register can also be used to sequentially program the Individual Address area of the

EEPROM, that is normally protected from accidental Store operations.

This register will be used for EEPROM read and write only when the EEPROM SELECT bit in the Control Register is set. This allows generic EEPROM read and write routines that do not affect the basic setup of the LAN91C100.

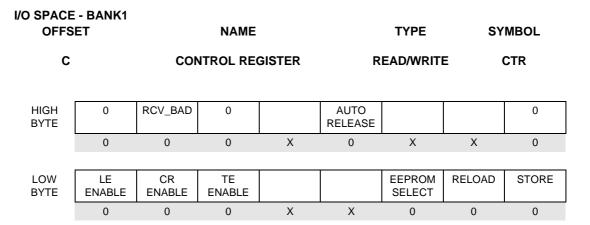

RCV\_BAD When set, bad CRC packets are received. When clear bad CRC packets do not generate interrupts and their memory is released.

AUTO RELEASE When set, transmit pages are released by transmit completion if the transmission was successful (when TX SUC is In that case there is no status word associated with its packet number, and successful packet numbers are not even written into the TX COMPLETION FIFO. A sequence of transmit packets will only generate an interrupt when the sequence is completely transmitted (TX EMPTY INT will be set), or when a packet in the sequence experiences a fatal error (TX INT will be set). Upon a fatal error TXENA is cleared and the transmission sequence stops. The packet number that failed is the present in the FIFO PORTS register, and its pages are not released, allowing the CPU to restart the sequence after corrective action is taken.

LE ENABLE Link Error Enable. When set it enables the LINK\_OK bit transition as one of the interrupts merged into the EPH INT bit. Defaults low (disabled). Writing this bit also serves as the acknowledge by clearing previous LINK interrupt conditions.

CR ENABLE Counter Roll over Enable. When set it enables the CTR\_ROL bit as one of the interrupts merged into the EPH INT bit. Defaults low (disabled).

TE ENABLE Transmit Error Enable. When set it enables Transmit Error as one of the interrupts merged into the EPH INT bit. Defaults low (disabled). Transmit Error is any condition that clears TXENA with TX\_SUC staying low as described in the EPHSR register.

EEPROM SELECT This bit allows the CPU to specify which registers the EEPROM RELOAD or STORE refers to. When high, the General Purpose Register is the only register read or written. When low, RELOAD reads Configuration, Base and Individual Address, and STORE writes the Configuration and Base registers.

RELOAD When set, it will read the EEPROM and update relevant registers with its contents. Clears upon completing the operation.

STORE When set, stores the contents of all relevant registers in the serial EEPROM. Clears upon completing the operation.

Note: When an EEPROM access is in progress the STORE and RELOAD bits will be read back as high. The remaining 14 bits of this register will be invalid. During this time attempted read/write operations, other than polling the

EEPROM status, will NOT have any effect on the internal registers. The CPU can resume accesses to the LAN91C100 after both bits are low. A worst case RELOAD operation initiated by RESET or by software takes less than  $750\mu\text{sec.}$

| I/O | <b>SPACE - BANK2</b> |

|-----|----------------------|

|     |                      |

OFFSET NAME TYPE SYMBOL

0 MMU COMMAND REGISTER WRITE ONLY MMUCR BUSY Bit

Readable

This register is used by the CPU to control the memory allocation, de-allocation, TX FIFO and RX FIFO control. The three command bits determine the command issued as described below:

| HIGH<br>BYTE |         |   |   |   |   |    |    |         |

|--------------|---------|---|---|---|---|----|----|---------|

|              |         |   |   |   |   |    |    |         |

| LOW<br>BYTE  | COMMAND |   |   | 0 | 0 | N2 | N1 | N0/BUSY |

|              | Х       | у | Z |   |   |    |    |         |

|              |         |   |   |   |   |    |    | 0       |

#### COMMAND SET

xyz

- 000 0) NOOP NO OPERATION

- 001 1) ALLOCATE MEMORY FOR TX N2,N1,N0 defines the amount of memory requested as (value + 1) \* 256 bytes. Namely N2,N1,N0 = 1 will request 2 \* 256 = 512 bytes. A shift-based divide by 256 of the packet length yields the appropriate value to be used as N2,N1,N0. Immediately generates a completion code at the ALLOCATION RESULT REGISTER. Can optionally generate an interrupt on successful completion. N2,N1,N0 are ignored by the LAN91C100 but should be implemented in the LAN91C100's software drivers for LAN9000 compatibility.

- 010 2) RESET MMU TO INITIAL STATE Frees all memory allocations, clears relevant interrupts, resets packet FIFO pointers.

- 011 3) REMOVE FRAME FROM TOP OF RX FIFO To be issued after CPU has completed processing of present receive frame. This command removes the receive packet number from the RX FIFO and brings the next receive frame (if any) to the RX area (output of RX FIFO).

- 100 4) REMOVE AND RELEASE TOP OF RX FIFO Like 3) but also releases all memory used by the packet presently at the RX FIFO output.

- 101 5) RELEASE SPECIFIC PACKET Frees all pages allocated to the packet specified in the PACKET NUMBER REGISTER. Should not be used for frames pending transmission. Typically used to remove transmitted frames, after reading their completion status. Can be used following 3) to release receive packet memory in a more flexible way than 4).

- 110 6) ENQUEUE PACKET NUMBER INTO TX FIFO This is the normal method of transmitting a packet just loaded into RAM. The packet number to be enqueued is taken from the PACKET NUMBER REGISTER.

- 111 7) RESET TX FIFOs This command will reset both TX FIFOs--theTX FIFO holding the packet numbers awaiting transmission and the TX Completion FIFO. This command provides a mechanism for canceling packet transmissions, and reordering or bypassing the transmit queue. The RESET TX FIFOs command should only be used when the transmitter is disabled. Unlike the RESET MMU command, the RESET TX FIFOs does not release any memory.

- Note 1: Bits N2,N1,N0 bits are ignored by the LAN91C100 but should be used for Command 0) to preserve software compatibility with the LAN91C92 and future devices. They should be zero for all other commands.

- Note 2: When using the RESET TX FIFOS command, the CPU is responsible for releasing the memory associated with outstanding packets, or re-enqueuing them. Packet numbers in the completion FIFO can be read via the FIFO ports register before issuing the command.

- Note 3: MMU commands releasing memory (commands 4 and 5) should only be issued if the corresponding packet number has memory allocated to it.

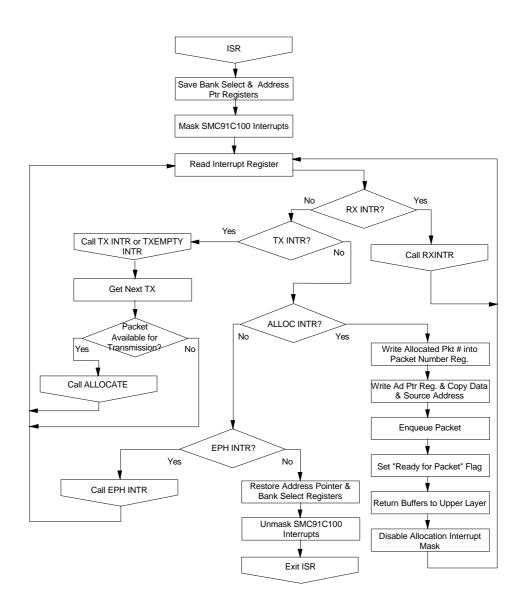

#### **COMMAND SEQUENCING**

A second allocate command (command 1) should not be issued until the present one has completed. Completion is determined by reading the FAILED bit of the allocation result register or through the allocation interrupt.

A second release command (commands 4, 5) should not be issued if the previous one is still being processed. The BUSY bit indicates that a release command is in progress. After issuing

command 5, the contents of the PNR should not be changed until BUSY goes low. After issuing command 4, command 3 should not be issued until BUSY goes low.

BUSY BIT Readable at bit 0 of the MMU command register address. When set indicates that MMU is still processing a release command. When clear, MMU has already completed last release command. BUSY and FAILED bits are set upon the trailing edge of command.

# I/O SPACE - BANK2 OFFSET

NAME

**TYPE**

**SYMBOL**

2

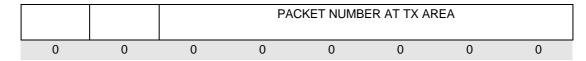

**PACKET NUMBER REGISTER**

READ/WRITE

PNR

PACKET NUMBER AT TX AREA - The value written into this register determines which packet number is accessible through the TX area. Some MMU commands use the number

stored in this register as the packet number parameter. This register is cleared by a RESET or a RESET MMU Command.

OFFSET NAME

**TYPE**

SYMBOL

3 ALLOCATION RESULT REGISTER

READ ONLY

ARR

This register is updated upon an ALLOCATE MEMORY MMU command.

| FAILED |   |   | ALL | OCATED PA | CKET NUME | BER |   |

|--------|---|---|-----|-----------|-----------|-----|---|

| 1      | 0 | 0 | 0   | 0         | 0         | 0   | 0 |

FAILED A zero indicates a successful allocation completion. If the allocation fails the bit is set and only cleared when the pending allocation is satisfied. Defaults high upon reset and reset MMU command. For polling purposes, the ALLOC\_INT in the Interrupt Status Register should be used because it is synchronized to the read operation. Sequence:

- 1) Allocate Command

- 2) Poll ALLOC\_INT bit until set

- 3) Read Allocation Result Register

ALLOCATED PACKET NUMBER Packet number associated with the last memory allocation request. The value is only valid if the FAILED bit is clear.

Note: For software compatibility with future versions, the value read from the ARR after an allocation request is intended to be written into the PNR as is, without masking higher bits (provided FAILED = 0).

I/O SPACE - BANK2

OFFSET NAME TYPE SYMBOL

4 FIFO PORTS REGISTER READ ONLY FIFO

This register provides access to the read ports of the Receive FIFO and the Transmit completion FIFO. The packet numbers to be processed by the interrupt service routines are read from this register.

| HIGH<br>BYTE | REMPTY |   | RX FIFO PACKET NUMBER |   |            |           |   |   |

|--------------|--------|---|-----------------------|---|------------|-----------|---|---|

|              | 1      | 0 | 0                     | 0 | 0          | 0         | 0 | 0 |

|              |        |   |                       |   |            |           |   |   |

| LOW<br>BYTE  | TEMPTY |   |                       | T | X DONE PAC | KET NUMBE | R |   |

|              | 1      | 0 | 0                     | 0 | 0          | 0         | 0 | 0 |

REMPTY No receive packets queued in the RX FIFO. For polling purposes, uses the RCV\_INT bit in the Interrupt Status Register.

TOP OF RX FIFO PACKET NUMBER Packet number presently at the output of the RX FIFO. Only valid if REMPTY is clear. The packet is removed from the RX FIFO using MMU Commands 3) or 4).

TEMPTY No transmit packets in completion queue. For polling purposes, uses the TX\_INT bit in the Interrupt Status Register.

TX DONE PACKET NUMBER Packet number presently at the output of the TX Completion FIFO. Only valid if TEMPTY is clear. The packet is removed when a TX INT acknowledge is issued.

Note: For software compatibility with future versions, the value read from each FIFO register is intended to be written into the PNR as is, without masking higher bits (provided TEMPTY and REMPTY = 0 respectively).

| I/O SPACE - BANK2<br>OFFSET |     |               | NAME      |        |              | TYPE                                      | SY        | MBOL |

|-----------------------------|-----|---------------|-----------|--------|--------------|-------------------------------------------|-----------|------|

| 6                           |     | PO            | INTER REG | GISTER | NC           | EAD/WRITE<br>OT EMPTY is<br>read only bit | 3         | PTR  |

| HIGH<br>BYTE                | RCV | AUTO<br>INCR. | READ      | ETEN   | NOT<br>EMPTY | РО                                        | INTER HIG | SH   |

|                             | 0   | 0             | 0         | 0      | 0            | 0                                         | 0         | 0    |

| LOW<br>BYTE                 |     |               |           | POINTE | R LOW        |                                           |           |      |

|                             | 0   | 0             | 0         | 0      | 0            | 0                                         | 0         | 0    |

POINTER REGISTER The value of this register determines the address to be accessed within the transmit or receive areas. It will auto-increment on accesses to the data register when AUTO INCR. is set. The increment is by one for every byte access, by two for every word access, and by four for every double word access. When RCV is set, the address refers to the receive area and uses the output of RX FIFO as the packet number, when RCV is clear the address refers to the transmit area and uses the packet number at the Packet Number Register.

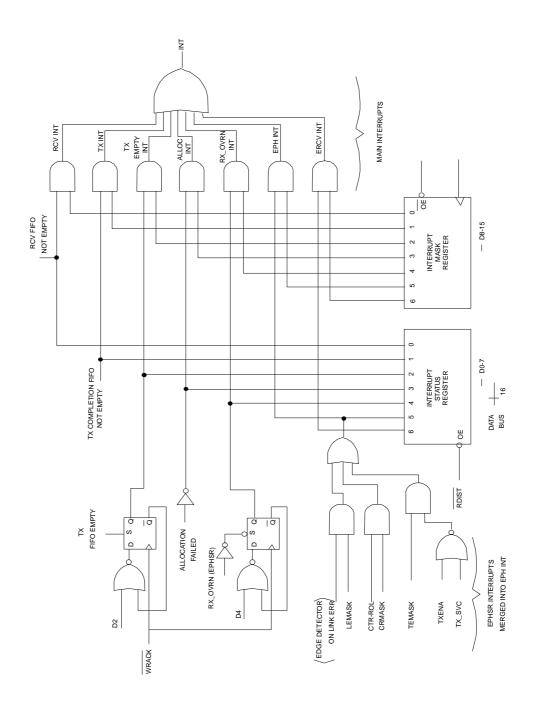

READ Determines the type of access to follow. If the READ bit is high, the operation intended is a read. If the READ bit is low, the operation is a write. Loading a new pointer value, with the READ bit high, generates a pre-fetch into the Data Register for read purposes.